# WESTERN DIGITAL

PRONTO ELECTRONIC SYSTEMS LTD. 466-478 CRANBROOK ROAD GANTS HILL, ILFORD 33500402 61.5 TEEBPHONE-01-55-5222

# WD279X-02 Floppy Disk Formatter/Controller Family

#### **FEATURES**

- . ON-CHIP PLL DATA SEPARATOR

- ON-CHIP WRITE PRECOMPENSATION LOGIC

- SINGLE +5V SUPPLY

- ACCOMMODATES SINGLE AND DOUBLE DENSITY FORMATS

IBM 3740 (FM) IBM 34 (MFM)

- . AUTOMATIC SEEK WITH VERIFY

- . MULTIPLE SECTOR READ/WRITE

- . TTL COMPATIBLE

- PROGRAMMABLE CONTROL

SELECTABLE TRACK-TO-TRACK ACCESS

HEAD LOAD TIMING

- SOFTWARE COMPATIBLE WITH THE FD179X SERIES

- SOFT SECTOR FORMAT COMPATIBILITY

#### **APPLICATIONS**

8" FLOPPY AND 51/4" MINI FLOPPY CONTROLLER SINGLE OR DOUBLE DENSITY CONTROLLER/FORMATTER The WD279X Family are MOS/LSf devices which perform the functions of a Floppy Dick Controller/Formatter. Software compatible with its predecessor, the FD179X, the device also contains a high performance Phase-Lock-Loop Data Separator as well as Write Precompensation Logic.

When operating in Double Density mode, Write Precompensation is automatically engaged to a value programmed via an external potentiometer. An on-chip VCO and phase comparator allows adjustable frequency range for 5¼ " or 8" Floppy Disk interfacing.

The WD279X is fabricated in NMOS silicon gate technology and available in a 40 pin dual-in-line ceramic or plastic package.

| FEATURES             | 2791 | 2793 | 2795 | 2797 |

|----------------------|------|------|------|------|

| Single Density (FM)  | x    | х    | х    | X    |

| Double Density (MFM) | l x  | X    | l x  | x    |

| True Data Bus        |      | X    |      | X    |

| Inverted Data Bus    | x    |      | x i  | .,   |

| Side Salect Out      |      |      | x    | x    |

| Internal CLK Divide  | x    | x    |      |      |

Figure 1.

STATUS

November, 1982

57 - not ready (1)

56 - Write plot (1)

55 - RTYPR

54 - RNF

53 - CRC

51 - Lody DRA studius (intr)

59 - Basy

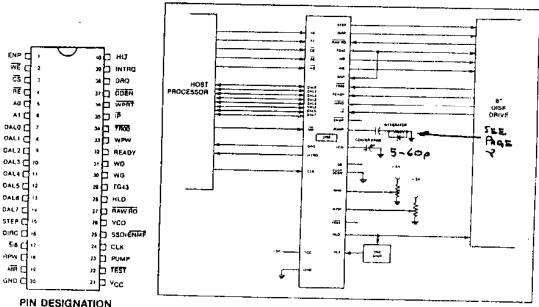

#### PIN OUTS

| PIN<br>NUMBER    | PIN NAME              | SYMBOL    | FUNCTION                                                                                                                                                                                                                                                                                                                                     |

|------------------|-----------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | ENABLE PRECOMP        | ENP       | A Logic high on this input enables write precomper sation to be performed on the Write Data output.                                                                                                                                                                                                                                          |

| 19               | MASTER RESET          | MR        | A logic low (50 microseconds min.) on this Inpuresets the device and loads HEX 03 into the command register. The Not Ready (Status Bit 7) is reseduring MR ACTIVE. When MR is brought to a logic high a RESTORE Command is executed, regardless of the state of the Ready signal from the drive. Also HEX 01 is loaded into sector register. |

| 20               | POWER SUPPLIES        | vss       | Ground                                                                                                                                                                                                                                                                                                                                       |

| 21               |                       | Vcc       | +5V ±5%                                                                                                                                                                                                                                                                                                                                      |

| COMPUTER IN      | I<br>TERFACE:         | İ         |                                                                                                                                                                                                                                                                                                                                              |

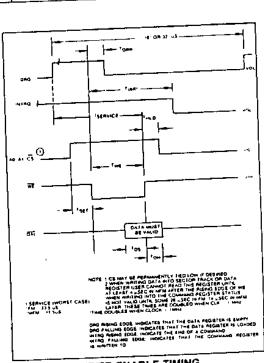

| 2                | WAITE ENABLE          | WE ·      | A logic low on this input gates data on the DAL into the selected register when CS is low.                                                                                                                                                                                                                                                   |

| 3                | CHIP SELECT           | ঙ্গে      | A logic low on this input selects the chip and enable computer communication with the device.                                                                                                                                                                                                                                                |

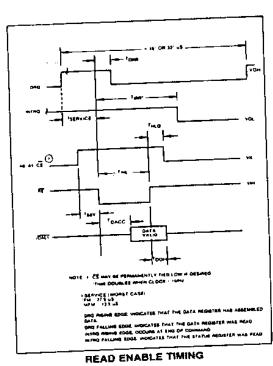

| 4                | READ ENABLE           | ĀĒ        | A logic low on this input controls the placement of data from a selected register on the DAL when CS is low.                                                                                                                                                                                                                                 |

| 5, 6             | AEGISTER SELECT LINES | A0, A1    | These inputs select the register to receive/transfe data on the DAL lines under RE and WE control:                                                                                                                                                                                                                                           |

|                  |                       |           | CS A1 A0 FE WE                                                                                                                                                                                                                                                                                                                               |

|                  |                       | :         | 0 0 0 Status Reg Command Reg<br>0 0 1 Track Reg Track Reg<br>0 1 0 Sector Reg Sector Reg<br>0 1 1 Data Reg Data Reg                                                                                                                                                                                                                          |

| 7-14             | DATA ACCESS LINES     | DALO-DAL7 | Eight bit bi-directional bus used for transfer of commands, status, and data. These lines are inverted (active low) on WD2791 and WD2795.                                                                                                                                                                                                    |

| 24               | CLOCK                 | CLK       | This input requires a free-running 50% duty cycle square wave clock for internal timing reference, 3 MHz ± 1% for mini flopples.                                                                                                                                                                                                             |

| 38               | data request          | DRO       | This output Indicates that the Data Register contains assembled data in Read operations, or the DR is empty in Write operations. This signal is reset when serviced by the computer through reading or loading the DR.                                                                                                                       |

| 39               | INTERRUPT REQUEST     | DRTMI     | This output is set at the completion of any command and is reset when the Slatus register is read or the Command register is written to.                                                                                                                                                                                                     |

| <br>  Loppy Disk | NTERFACE:             |           |                                                                                                                                                                                                                                                                                                                                              |

| 15               | STEP                  | STEP      | The step output contains a pulse for each step.                                                                                                                                                                                                                                                                                              |

| 16               | DIRECTION             | DIRC      | Direction Output is active high when stepping in, active low when stepping out.                                                                                                                                                                                                                                                              |

| 17               | 514," 8" SELECT       | 5/8       | This input selects the internal VCO frequency for use with 5¼ * drives or 8* drives.                                                                                                                                                                                                                                                         |

| 18               | READ PULSE WIDTH      | RPW       | An external potentiometer tied to this input controls the phase comparator within the data separator.                                                                                                                                                                                                                                        |

| PIN    |                                    |          | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------|------------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NUMBER | PIN NAME                           | SYMBOL   | A legis low on this input allows adjustment of exter-                                                                                                                                                                                                                                                                                                                                                                                                          |

| 22     | TEST                               | TEST     | nat resistors by enabling internal signals to appear on selected pins.                                                                                                                                                                                                                                                                                                                                                                                         |

| 23     | РИМР                               | PUMP     | High-impedance output signal which is forced high or low to increase/decrease the VCO frequency.                                                                                                                                                                                                                                                                                                                                                               |

| 25     | ENABLE MINI-FLOPPY<br>(2791, 2793) | ENMF     | A logic low on this input enables an internal +2 of the Master Clock. This allows both 5¼" and 8" drive operation with a single 2 MHz clock. For a 1 MHz clock on Pin 24, this line must be left open or tied to a Logic 1.                                                                                                                                                                                                                                    |

| 25     | SIDE SELECT OUTPUT<br>(2795, 2797) | sso      | The logic level of the Side Select Output is directly controlled by the 'S' flag in Type II or III commands. When U = 1, SSO is set to a logic 1. When U = 0, SSO is set to a logic 0. The SSO is compared with the side information in the Sector i.D. Field. If they do not compare Status Bit 4 (RNF) is set. The Side Select Output is only updated at the beginning of a Type II or III command. It is forced to a logic 0 upon a MASTER RESET condition. |

| 26     | VOLTAGE-CONTROLLED OSCILLATOR      | vco      | An external capacitor tied to this pin adjusts the VCO center frequency.                                                                                                                                                                                                                                                                                                                                                                                       |

| 27     | RAW READ                           | RAW READ | The data Input signat directly from the drive. This input shall be a negative pulse for each recorded flux transition.                                                                                                                                                                                                                                                                                                                                         |

| 28     | HEAD LOAD                          | HLD      | The HLD output controls the loading of the Read-<br>Write head against the media.                                                                                                                                                                                                                                                                                                                                                                              |

| 29     | TRACK GREATER THAN 43              | TG43     | This output informs the drive that the Read/Write head is positioned between tracks 44-76. This output is valid only during Read and Write Commands.                                                                                                                                                                                                                                                                                                           |

| 30     | WRITE GATE                         | wg       | This output is made valid before writing is to be performed on the diskette.                                                                                                                                                                                                                                                                                                                                                                                   |

| 31     | WRITE DATA                         | WD       | MFM or FM output pulse per flux transition. WE contains the unique Address marks as well as data and clock in both FM and MFM formats.                                                                                                                                                                                                                                                                                                                         |

| 32     | READY                              | READY    | This input indicates disk readiness and is sampled for a logic high before Read or Write commands are performed. If Ready is low the Read or Write operation is not performed and an interrupt in generated. Type it operations are performed regard less of the state of Ready. The Ready input appears in inverted format as Status Register bit 7.                                                                                                          |

| 33     | WRITE PRECOMP                      | WPW      | An external potentiometer fied to this input control the amount of delay in Write precompensation mode                                                                                                                                                                                                                                                                                                                                                         |

| 34     | TRACK 00                           | TROO     | This input informs the WD279X that the Read/Writhhead is positioned over Track 00.                                                                                                                                                                                                                                                                                                                                                                             |

| 35     | INDEX PULSE                        | ĪΡ       | This input informs the WD279X when the index hot is encountered on the diskette.                                                                                                                                                                                                                                                                                                                                                                               |

| PIN NUMBER       | PIN NAME         | SYMBOL | FUNCTION                                                                                                                                                |  |  |  |

|------------------|------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 36 WRITE PROTECT |                  | WPRT   | This input is sampled whenever a Write Comman received. A logic low terminates the command sets the Write Protect Status bit.                           |  |  |  |

| 37               | DOUBLE DENSITY   | DOEN   | This input pin selects either single or double density operation. When DDEN = 0, double density is selected. When DDEN = 1, single density is selected. |  |  |  |

| 40               | HEAD LOAD TIMING | ни     | When a logic high is found on the HLT input the head is assumed to be engaged. It is typically derived from a 1 shot triggered by HLD.                  |  |  |  |

#### GENERAL DESCRIPTION

The WD279X are N-Channel Silicon Gate MOS LSI devices which perform the functions of a Floppy Disk Formatter/Controller in a single chip implementation. The WD279X, which can be considered the end result of both the FD1771 and FD179X designs, Is IBM 3740 compatible in single density mode (FM) and System 34 compatible in Double Censity Mode (MFM). The WD279X contains all the features of its predecessor the FD179X plus a high performance Phase-Lock-Loop Data Separator as well as Write Precompensation Logic, in Double Density mode, Write Precompensation is automatically engaged to a value programmed via an external potentiometer. In order to maintain compatibility, the FD1771, FD179X and WD279X designs were made as close as possible with the computer interface, instruction set, and VO registers being identical Also, head load control is identical. In each case, the actual pin assignments vary by only a few pins from any one to another.

The processor interface consists of an 8-bit bl-directional bus for data, status, and control word transfers. The WO279X is set up to operate on a multiplexed bus with other bus-oriented devices.

The WD279X is TTL compatible on all inputs and outputs. The outputs will drive one TTL load or three LS loads. The 2793 is identical to the 2791 except the DAL lines are TRUE for systems that utilize true data busses.

The 2795/7 has a side select output for controlling doubte sided drives.

#### ORGANIZATION

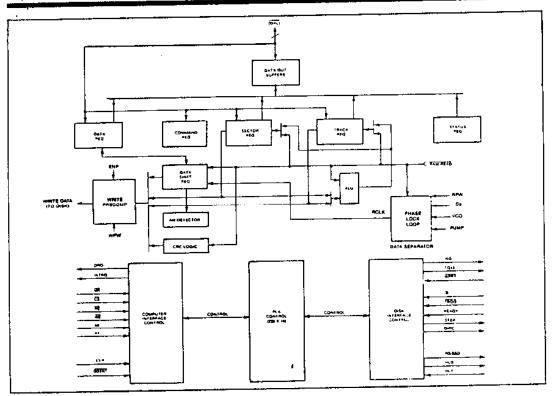

The Floppy Disk Formatter block diagram is illustrated on page 5. The primary sections include the parallel processor interface and the Floppy Disk interface.

Data Shift Register — This 8-bit register assembles serial data from the Read Data input (RAW READ) during Read operations and transfers serial data to the Write Data output during Write operations.

Data Register — This 8-bit register is used as a holding register during Disk Read and Write operations in Disk Read operations the assembled data byte is transferred in parallel to the Data Register from the Data Shift Register. In Disk Write operations information is transferred in parallel from the Data Register to the Data Shift Register.

When executing the Seek command the Dala Register holds the address of the desired Track position. This

register is loaded from the DAL and gated onto the DAL under processor control.

Track Register — This 8-bit register holds the track number of the current Read/Write head position. It is incremented by one every time the head is stepped in (towards track 76, and decremented by one when the head is stepped out (towards track 00). The contents of the register are compared with the recorded track number in the ID fleid during disk Read, Write and Verify operations. The Track Register can be loaded from or transferred to the DAL. This Register should not be loaded when the device is busy.

Sector Register (SR) — This 8-bit register holds the address of the desired sector position. The contents of the register are compared with the recorded sector number in the ID field during disk Read or Write operations. The Sector Register contents can be loaded from or transferred to the DAL. This register should not be loaded when the device is busy.

Command Register (CR) — This 8-bit register holds the command presently being executed. This register should not be loaded when the device is busy unless the new command is a force interrupt. The command register can be loaded from the DAL, but not read onto the DAL.

Status Register (STR) — This 8-bit register holds device Status information. The meaning of the Status bits is a function of the type of command previously executed. This register can be read onto the DAL, but not loaded from the DAL.

CRC Logic — This logic is used to check or to generate the 16-bit Cyclic Redundancy Check (CRC). The polynomial is:  $G(x) = x^{16} + x^{12} + x^5 + 1$ .

The CRC includes all Information starting with the address mark and up to the CRC characters. The CRC register is preset to ones prior to data being shifted through the circuit.

Arithmetic/Logic Unit (ALU) — The ALU is a serial comparator, incrementer, and decrementer and is used for register modification and comparisons with the disk recorded ID

Timing and Control — All computer and Floppy Olsk interface controls are generated through this logic. The internal device timing is generated from an external crystal clock.

AM Detector — The address mark detector detects ID, data and Index address marks during read and write operations.

Write Precompensation — enables write precompensation to be performed on the Write Data output.

WD279X BLOCK DIAGRAM

Data Separator — a high performance Phase-Lock-Loop Data Separator with on-chip VCO and phase comparator allows adjustable frequency range for 5¼ or 8" Floppy Disk interfacing.

#### PROCESSOR INTERFACE

The interface to the processor is accomplished through the eight Data Access Lines (DAL) and associated control signals. The DAL are used to transfer Data, Status, and Control words out of, or into the WD279X. The DAL are three state buffers that are enabled as output drivers when Chip Select (CS) and Read Enable (RE) are active (low togic state) or act as input receivers when CS and Write Enable (WE) are active.

When transfer of data with the Floppy Dlsk Controller is required by the host processor, the device address is decoded and  $\overline{CS}$  is made low. The address bits A1 and A0, combined with the signals  $\overline{RE}$  during a Read operation or  $\overline{WE}$  during a Write operation are interpreted as selecting the following registers:

| A1  | - A0 | READ (RE)       | WRITE (WE)       |

|-----|------|-----------------|------------------|

| 0   | 0    | Status Register | Command Register |

| 0   | 1    | Track Register  | Track Register   |

| Ιı  | 0    | Sector Register | Sector Register  |

| 1 1 | 1    | Data Register   | Data Register    |

|     |      |                 |                  |

During Direct Memory Access (DMA) types of data transfers between the Data Register of the WD279X and the processor, the Data Request (DRQ) output is used in Data Transfer control. This signal also appears as status bit 1 during Read and Write operations.

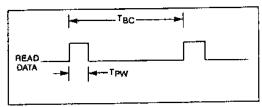

On Disk Read operations the Data Request is activated (set high) when an assembled serial input byte is transferred in parallel to the Data Register. This bit is cleared when the Data Register is read by the processor, if the Data Register is read after one or more characters are lost, by having new data transferred into the register prior to processor readout, the Lost Data bit is set in the Status Register. The Read operation continues until the end of sector is reached.

On Disk Write operations the data Request is activated when the Data Register transfers its contents to the Data Shift Register, and requires a new data byte. It is reset when the Data Register is loaded with new data by the processor, it new data is not loaded at the time the next serial byte is required by the Floppy Disk, a byte of zeroes is written on the diskette and the Lost Data bit is set in the Status-Register.

At the completion of every command an INTRO is generated. INTRO is reset by either reading the status register or by loading the command register with a new command. In addition, INTRO is generated if a Force Interrupt command condition is met.

The 279X has two modes of operation according to the state of ODEN (Pin 37). When ODEN = 1, Single Density (FM) is selected. When ODEN = 0, Double Density (MFM) is selected. In either case, the CLK input (Pin 24) is set at 2 MHz for 8" drives or 1 MHz for 51/4" drives.

On the 2791/2793, the ENMF Input (Pin 25) can be used for controlling both 5¼" and 8" drives with a single 2 MHz clock, When ENMF = 0, an internal + 2 of the CLK is performed. When ENMF = 1, no divide takes place. This allows the use of a 2 MHz clock for both 5¼" and 8" configurations.

The internal VCO frequency must also be set to the proper value. The 5/8 input (Pin 17) is used to select data separator operation by internally dividing the Read Clock, When 5/8 = 0, 51/4" data separation is selected; when 5/8 = 1, 8" drive data separation is selected.

| CLOCK (24) | ENMF (25) | 5/8 (17) | DRIVE  |

|------------|-----------|----------|--------|

| 2 MHz      | 1         | 1        | 8"     |

| 2 MHz      | 0.        | 0        | 51/4"  |

| 1 MHz      | 1         | 0        | 51/4 * |

Note: All other conditions invalid.

#### **FUNCTIONAL DESCRIPTION**

The WD279X-02 is software compatible with the FD179X-02 series of Floppy Disk Controllers. Commands, status, and data transfers are performed in the same way. Software generated for the 179X can be transferred to a 279X system without modification.

In addition to the 179X, the 279X contains an internal Data Separator and Write precompensation circuit. The TEST (Pin 22) line is used to adjust both data separator and precompensation. When TEST = 0, the WD (Pin 31) line is internally connected to the output of the write precompone-shot. Adjustment of the WPW (Pin 33) line can then be accomplished. A second one-shot tracks the precomp setting at approximately 3:1 to insure adequate Write Data pulse widths to meet drive specifications.

Similarly, Data separation is also adjusted with TEST = 0. The TG43 (Pin 29) line is internally connected to the output of the read data one-shot, which is adjusted via the RPW (Pin 18) line. The DIRC (Pin 18) line contains the Read Clock output (.5 MHz for 8" drives). The VCO Trimming capacitor (Pin 26) is adjusted for center frequency.

Internal timing signals are used to generate pulses during the adjustment mode so that these adjustments can be made while the device is in-circuit. The TEST line also contains a pull-up resistor, so adjustments can be performed simply by grounding the TEST pin, overriding the pull-up. The TEST pin cannot be used to disable stepping rates during operation as its function is quite different from the test of the test of the start of the start of the test of the start of the start of the test of

Other pins on the device also include pull-up resistors and may be left open to satisfy a Logic 1 condition. These are: ENP, \$/8, ENMF, WPRT, DOEN, HLT, TEST, and MR.

#### GENERAL DISK READ OPERATIONS

Sector lengths of 128, 256, 512 or 1024 are obtainable in either FM or MFM formats. For FM, CDEN should be placed to logical "1." For MFM formats, DDEN should be

| Sector L                     | ength Table*                           |

|------------------------------|----------------------------------------|

| Sector Length<br>Field (hex) | Number of Bytes<br>in Sector (decimal) |

| 00                           | 128                                    |

| 01                           | 256                                    |

| 02                           | 512                                    |

| 03                           | 1024                                   |

<sup>2795/97</sup> may vary — see command summary.

placed to a logical "0." Sector lengths are determined at format time by the fourth byte in the "10" field.

The number of sectors per track as far as the 279X is concerned can be from 1 to 255 sectors. The number of tracks as far as the 279X is concerned is from 0 to 255 tracks. For IBM 3740 compatibility, sector lengths are 128 bytes with 28 sectors per track. For System 34 compatibility (MFM), sector lengths are 256 bytes/sector with 26 sectors/track; or lengths of 1024 bytes/sector with 8 sectors/track.

#### **GENERAL DISK WRITE OPERATION**

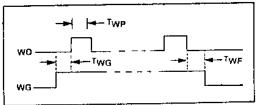

When writing is to take place on the diskette the Write Gate (WG) output is activated, allowing current to flow into the Read/Write head. As a precaution to erroneous writing the first data byte must be loaded into the Data Register in response to a Data Request from the 279X before the Write Gate signal can be activated.

Writing is inhibited when the Write Protect Input is a logic low, in which case any Write command is immediately terminated, an interrupt is generated and the Write Protect status bit is set.

For write operations, the 279X provides Write Gate (Pin 30) and Write Data (Pin 31) outputs. Write data consists of a series of pulses set to a width approximately three times greater than the precomp adjustment. Write Data provides the unique address marks in both formats.

#### READY

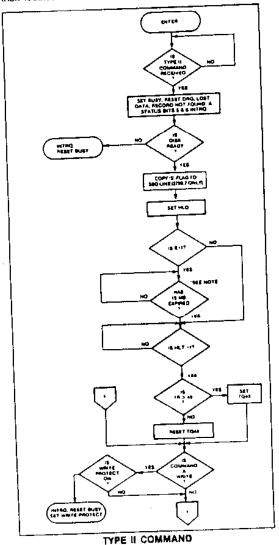

Whenever a Read or Write command (Type If or III) is received the 279X samples the Ready input. If this input is logic low the command is not executed and an interrupt is generated. All Type I commands are performed regardless of the state of the Ready input. Also, whenever a Type II or III command is received, the TG43 signal output is updated. TG43 may be tiled to ENP to enable write precompensation on tracks 44-76.

#### COMMAND DESCRIPTION

The WD279X witt accept eleven commands. Command words should only be loaded in the Command Register when the Busy status bit is off (Status bit 0). The one exception is the Force interrupt command. Whenever a command is being executed, the Busy status bit is set. When a command is completed, an interrupt is generated and the Busy status bit is reset. The Status Register indicates whether the completed command encountered an error or was fault free, For ease of discussion, commands are divided into four types. Commands and types are summarized in Table 1.

### TABLE 1. COMMAND SUMMARY

| A CZ | mmands for Models:                      | 2791, 279 | 33  |   |     |        |    |                |      | B. Co | mmai | nds fo | r Mode   | 91s: 27 | 95, 27 | 97   |    |

|------|-----------------------------------------|-----------|-----|---|-----|--------|----|----------------|------|-------|------|--------|----------|---------|--------|------|----|

|      | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |           |     |   | BI  | ts     |    |                |      |       |      |        | Bi       | ts      |        |      |    |

| Type | Command                                 | 7         | 6   | 5 | 4   | 3      | 2  | 1_             | 0    | 7     | 8    | 5      | 4        | 3       | 2      | _ 1  | 0  |

| 7    | Restore                                 | 0         | n   | a | 0   | _<br>_ |    | 14             | rO.  | 0     | 0    | 0      | 0        | h       | ٧      | Γţ   | ra |

| -    | Seek                                    | ŏ         | ŏ   | ō | i   | h      | V  | F1             | ro   | 0     | 0    | 0      | 1        | h       | V      | ۲1   | 70 |

| :    |                                         | ň         | ň   | 1 | Т   | h      | V  | r <sub>1</sub> | ro l | 0     | 0    | 1      | 7        | ħ       | ٧      | 11   | r0 |

| !    | Step                                    |           | ·   | ń | ÷   | h      | ù  | r1             | ro   | ١٥    | 1    | 0      | Ť        | h       | V      | (1   | η  |

| t    | Step-in                                 | ŭ         | - ! | • | ÷   |        | v  | ri             | ro   | ìò    | 1    | 1      | т        | h       | V      | Fţ   | rc |

| ţ    | Step-out                                | 0         | 1   | 1 | '   | ħ      | ¥. | •              | -    | I .   | 'n   | ò      | m        | ï       | É      | U    | 0  |

| П    | Read Sector                             | 1         | 0   | 0 | m   | S      | E  | C              | 0    | l :   | Ü    |        |          |         | Ē      | ŭ    | a, |

| 11   | Write Sector                            | 1         | 0   | 1 | (T) | S      | E  | С              | aŋ   | ו ן   | U    | 1      | m        | _       |        |      | C  |

| III  | Read Address                            | 1         | 1   | 0 | 0   | 0      | E  | 0              | 0    | 1     | 1    | 0      | 0        | 0       | 5      | · U  | -  |

|      | Read Track                              | 1         | 1   | 1 | 0   | 0      | E  | 0              | 0    | 1     | 1    | 1      | 0        | 0       | E      | U    | 0  |

| Ш    |                                         | :         |     | i | -   | ň      | F  | 0              | 0    | 1 1   | 1    | 1      | 1        | 0       | Ε      | U    | 0  |

| 111  | Write Track                             | 1         | !   |   |     | 10     | 12 | Ĭš             | ĺо   | 1 .   | •    | Ô      | 1        | 13      | 12     | - 11 | 10 |

| IV   | Force Interrupt                         | 1         | 1   | 0 | 1   | 13     | 12 | • 1            |      | ⊥'_   |      |        | <u> </u> |         |        |      |    |

### TABLE 2 FLAG SUMMARY

| Command<br>Type | Bit<br>No(s) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Description                                                                                |

|-----------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| l I             | 0, 1         | r1 r0 = Stepping Motor Rate<br>See Table 3 for Rate Summar)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ,                                                                                          |

| 1               | 2            | V = Track Number Verify Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | V = 0, No verify<br>V = 1, Verify on destination track                                     |

| ,               | 3            | h ≃ Head Load Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <ul> <li>n = 0, Unload head at beginning</li> <li>h = 1, Load head at beginning</li> </ul> |

| ı               | 4            | T = Track Update Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | T = 0, No update<br>T = 1, Update track register                                           |

| 11.8.11         | a            | ag = Data Address Mark                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | a0 = 0, FB (DAM)<br>a0 = 1, FB (deleted DAM)                                               |

| II              | 1            | C = Side Compare Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | C = 0, Disable side compare<br>C = 1, Enable side compare                                  |

| II & \$II)      | 1            | U = Update SSO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | U = 0, Update SSO to 0 U = 1, Update SSO to 1                                              |

| 98.00           | 2            | E = 15 MS Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | E = 0, No. 15 MS delay<br>E = 1, 15 MS delay (30 MS for 1 MHz)                             |

| H               | 3            | S = Side Comparé Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | S = 0, Compare for side 0<br>S = 1, Compare for side 1                                     |

| li              | 3            | L = Sector Length Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | USB's Sector Length in IO Field 00 01 10 11                                                |

| ,               |              | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | L = 0 256 512 1024 128<br>L = 1 128 256 512 1024                                           |

| U               | 4            | m ≖ Multiple Record Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | m = 0, Single record<br>m = 1, Multiple records                                            |

| IV .            | 0-3          | Ix = Interrupt Condition<br>  I0 = 1 Not Ready To Ready To Not Ready To | ady Transitlon<br>ady Transitlon<br>ipt, Requires A Reset*                                 |

<sup>\*</sup>NOTE: See Type IV Command Description for further information.

When operating in Double Density mode (DDEN = 0), the 279X has the capability of providing a user-defined precompensation value for Write Data. An external potentiometer (10K) tied to the WPW signal (Pin 33) allows a setting of 100 to 300 ns from nominal.

Setting the Write precomp value is accomplished by forcing the TEST line (Pin 22) to a Logic 0. A stream of pulses can then be seen on the Write Data (Pin 31) line. Adjust the WPW Potentiometer for the desired pulse width. This adjustment may be performed in-circuit since Write Gate (Pin 30) is inactive while TEST = 0.

#### **Data Separation**

The 279X can operate with either an external data separator or its own internal recovery circuits. The condition of the TEST line (Pin 22) in conjunction with MR (Pin 19) will select internal or external mode.

To program the 279X for external VCO, a MR pulse must be applled while TEST = 0. A clock equivalent to eight times the data rate (e.g., 4.0 MHz for 8" Double Density) is applied to the VCO input (Pin 26). The feedback reference voltage is available on the Pump output (Pin 23) for external integration to control the VCO. TEST is returned to a Logic 1 for normal operation. Note: To maintain this mode, TEST must be held low whenever MR is applied.

For internal VCO operation, the TEST line must be high during the MR pulse, then set to a Logic 0 for the adjustment procedure.

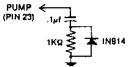

A 50K Potentiometer fied to the RPW Input (Pin 18) is used to set the internal Read Data pulse for proper phasing. With a scope on Pin 29 (TG43), adjust the RPW pulse for 1/8 of the data rate (250 ns for 8° Double Density). An external variable capacitor of 5-60 pf is tied to the VCO Input (Pin 28) for adjusting center frequency. With a Irequency counter on Fin 16 (DIRC) adjust the trimmer cap to yield the appropriate Data Rate (500 KHz for 8° Double Density). The DDEN line must be low while the 5/8 line is held high or the adjustment times above will be doubled.

After adjustments have been made, the TEST pin is returned to a Logic 1 and the device is ready for operation. Adjustments may be made in-circuit since the DIRC and TG43 lines may toggle without affecting the drive.

The PUMP output (Pin 23) consists of positive and negative pulses, which their duration is equivalent to the phase difference of incoming Data vs. VCO frequency. This signal is internally connected to the VCO input, but a Filter is needed to connect these pulses to a slow moving DC voltage.

The internal phase-detector is unsymmetrical for a random distribution of data pulses by a factor of two, in favor of a PUMP UP condition. Therefore, it is desirable to have a PUMP DOWN twice as responsive to prevent run-away during a lock attempt.

A first order lag-lead filter can be used at the PUMP output (Pin 23). This filter controls the instantaneous response of the VCO to bit-shifted data (jitter) as well as the response to normal frequency shift, i.e., the lock-up time. A balance must be accomplished between the two conditions to

inhibit over-responsiveness to litter and to prevent an extremely wide lock-up response, leading to PUMP runaway. The fitter affects these two reactions in mutually opposite directions.

The Source Impedance for a PUMP UP/DOWN condition is 600/120 ohms, respectively, therefore the change in bias voltage for each pump can be approximated:

$$dV = \frac{dt \Delta V}{RC} \qquad \qquad dt = 250 \text{ ns. (set by RPW)}$$

$$C = 0.1 \mu\text{f}$$

$$R = RS + R$$

$$\Delta V = 2.6 \text{ V for PUMP UP}$$

$$0.9 \text{V for PUMP DOWN}$$

Look up response (TL) is the transient time for the Loop to lock from center frequency (FO) to maximum lock range:

Where:

Ko = VCO Conversion Gain = 3.7KHz/mV

Ft = Lock Range = 4.00 MHz

ΔP = Change in Blas for each Pump = 4 mV/PUMP

400 KHz x 3.7 KHz x 4 mV = 27 pumps 27 pumps = 54 µsec = 3.4 Byte times (8" Double Density) The following Filter Circuit is recommended for 8" FM/MFM:

Since 5¼\* Drives operate at exactly one-half the data rate (250 Kb/sec) the above capacitor should be doubled to .2 or 22d.

#### TYPE I COMMANDS

The Type I Commands include the Restore, Seek, Step, Step-in, and Step-Out commands. Each of the Type I Commands contains a rate field (rg rt), which determines the stepping motor rate as defined in Table 3.

A  $2\mu s$  (MFM) or  $4\mu s$  (FM) pulse is provided as an output to the drive. For every step pulse issued, the drive moves one track location in a direction determined by the direction output. The chip will step the drive in the same direction it last stepped unless the command changes the direction.

The Direction signal is active high when stepping in and low when stepping out. The Direction signal is valid before the first stepping pulse is generated.

The rates (shown in Table 3) can be applied to a Step-Direction Motor through the device interface.

TABLE 3. STEPPING RATES

| C  | LK  | 2 MHz    | 1 MHz    |  |  |

|----|-----|----------|----------|--|--|

| R1 | RO. | TEST = 1 | TEST = 1 |  |  |

| 0  | 0   | 3 ms     | 6 ms     |  |  |

| 0  | 1   | 6 ms     | 12 ms    |  |  |

| 1  | 0   | 10 ms    | 20 ms    |  |  |

| 1  | 1   | .15 ms   | 30 ms    |  |  |

After the last directional step an additional 15 milliseconds of head settling time takes place if the Verify flag is set in Type I commands. Note that this time doubles to 30 ms for

a 1 MHz clock. There is also a 15 ms head settling time if the Effag is set in any Type II or III command.

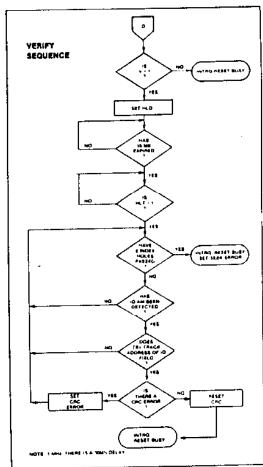

When a Seek, Step or Restore command is executed an optional verification of Read-Write head position can be performed by setting bit 2 (V = 1) in the command word to a logic 1. The verification operation begins at the end of the 15 millisecond settling time after the head is loaded against the media. The track number from the first encountered to Field is compared against the contents of the Track Register. If the track numbers compare and the 1D Field Cyclic Redundancy Check (CRC) is correct, the verify operation is complete and an INTRO is generated with no errors. If there is a match but not a valid CRC, the CRC error status bit is set (Status bit 3), and the next encountered ID field is read from the disk for the verification operation.

The WD279X must find an 4D field with correct track number and correct CRC within 5 revolutions of the media; otherwise the seek error is set and an INTRQ is generated. If V=0, no verification is performed.

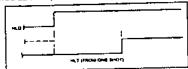

The Head Load (HLD) output controls the movement of the read/write head against the medla. HLD is activated at the beginning of a Type I command if the hillag is set (h = 1), at the end of the Type I command if the verify flag (V = 1), or upon receipt of any Type II or III command. Once HLD is active it remains active until either a Type I command is received with (h = 0 and V = 0); or if the 279X is in an idle state (non-busy) and 15 index pulses have occurred.

Head Load timing (HLT) is an input to the 279X which is used for the head engage time. When HLT = 1, the 279X assumes the head is completely engaged. The head engage time is typically 30 to 100 ms depending on drive. The low to high transition on HLD is typically used to fire a one shot. The output of the one shot is then used for HLT and supplied as an input to the 279X.

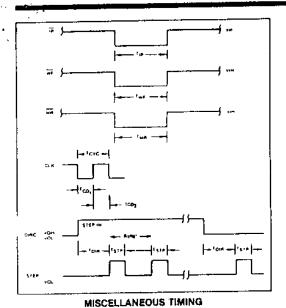

HEAD LOAD TIMING

When both HLD and HLT are true, the 279X will then read from or write to the media. The "and" of HLD and HLT appears as status Bit 5 in Type I status.

In summary for the Type I commands: if h=0 and V=0, HLD is reset. If h=1 and V=0, HLD is set at the beginning of the command and HLT is not sampled nor is there an internal 15 ms delay. If h=0 and V=1, HLD is set near the end of the command, an internal 15 ms occurs, and the 279X waits for HLT to be true. If h=1 and V=1, HLD is set at the beginning of the command. Near the end of the command, after all the steps have been issued, an internal 15 ms delay occurs and the 279X then waits for HLT to occur.

For Type II and III commands with E flag off, HLD is made active and HLT is sampled until true. With E flag on, HLD is made active, an Internal 15 ms delay occurs and then HLT is sampled until true.

#### RESTORE (SEEK TRACK 0)

Upon receipt of this command the Track 00 (TR00) Input Is sampled. If TR00 is active low indicating the Read-Write head is positioned over track 0, the Track Register is loaded with zeroes and an interrupt is generated. If TR00 is not active low, stepping pulses at a rate specified by the f100 held are issued until the TR00 input is activated. At this time the Track Register is loaded with zeroes and an interrupt is generated. If the TR00 input does not go active low after 255 stepping pulses, the 279X terminates operation, interrupts, and sets the Seek error status bit. A verification operation takes place if the V flag is set. The hilt allows the head to be loaded at the start of command. Note that the Restore command is executed when MR goes from an active to an inactive state.

#### SEEK

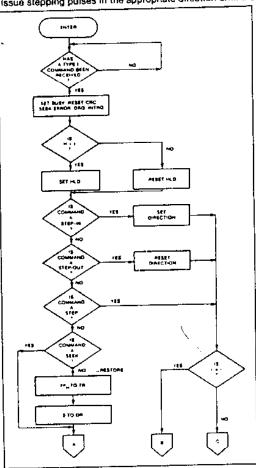

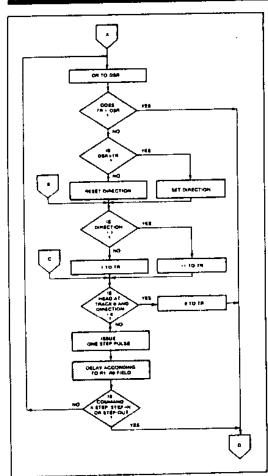

This command assumes that the Track Register contains the track number of the current position of the Head-Write head and the Data Register contains the desired track number. The WD279X will update the Track register and issue stepping pulses in the appropriate direction until the

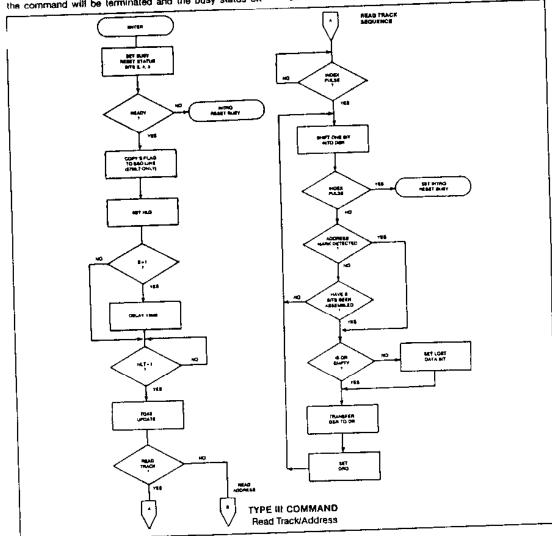

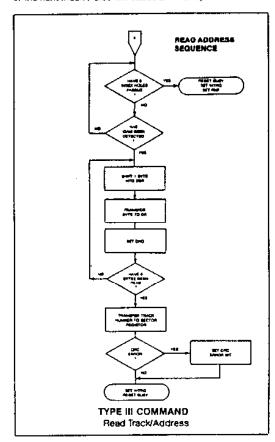

TYPE I COMMAND FLOW

TYPE I COMMAND FLOW

contents of the Track register are equal to the contents of the Data Register (the desired track location). A verification operation takes place if the V flag is on. The hibit allows the head to be loaded at the start of the command. An interrupt is generated at the completion of the command. Note: When using multiple drives, the track register must be updated for the drive selected before seeks are issued.

#### STEP

STUD Department of this command, the 279X issues one stepping pulse to the disk drive. The stepping motor direction is the same as in the previous step command. After a delay determined by the (1f0 field, a verification takes place if the V flag is on. If the T flag is on, the Track Register is updated. The h bit allows the head to be loaded at the start of the command. An interrupt is generated at the completion of the command.

#### STEP-IN

Upon receipt of this command, the 279X issues one stepping pulse in the direction towards track 78. If the T flag is on, the Track Register is incremented by one, After a

TYPE I COMMAND FLOW

delay determined by the f1f0 field, a verification takes place if the V flag is on. The h bit allows the head to be loaded at the start of the command. An interrupt is generated at the completion of the command.

#### STEP-OUT

Upon receipt of this command, the 279X Issues one stepping pulse in the direction towards track 0. If the T ilag is on, the Track Register is decremented by one. After a delay determined by the f1f0 field, a verification takes place if the V flag is on. The h bit allows the head to be loaded at the start of the command. An interrupt is generated at the completion of the command.

#### EXCEPTIONS